電界効果とその応用。 CCDとは

初めて、電子電荷を保存してから読み取るというアイデアを備えたCCDの原理は、メモリを置き換えることができるコンピュータ用の新しいタイプのメモリを探す過程で、60年代後半に2人のBELLエンジニアによって開発されました。 フェライトリング(はい-はい、そのような記憶がありました)。 このアイデアは有望ではないことが判明しましたが、シリコンが可視スペクトルの放射線に反応する能力に注目し、この原理を画像処理に使用するアイデアが開発されました。

用語の定義から始めましょう。

略語 CCD は「Charge-Coupled Devices」を意味します。この用語は、英語の「Charge-Coupled Devices (CCD)」から形成されました。

このタイプのデバイスは、現在、さまざまな分野で非常に幅広い用途があります。 光電子デバイス画像を登録します。 日常生活では、これらはデジタルカメラ、ビデオカメラ、さまざまなスキャナーです。

CCD受信機と、電気信号をピックアップするための感光領域と2つの電気接点を持つ従来の半導体フォトダイオードとの違いは何ですか?

初めに、CCDレシーバーには、数千から数十万、さらには数百万の、そのような感光領域(多くの場合、ピクセルと呼ばれます-光を受け取り、それを電荷に変換する要素)がたくさんあります。 個々のピクセルのサイズは同じで、単位から数十ミクロンまで可能です。 ピクセルは 1 行に並べることができます。受信機は CCD ラインと呼ばれ、表面領域を偶数行で埋めます。受信機は CCD マトリックスと呼ばれます。

受光素子の配列(長方形) 青色の) CCD ルーラーと CCD マトリックスで。

第二に、従来のマイクロ回路のように見えるCCDレシーバーには、電気信号を出力するための膨大な数の電気接点はありません。電気信号は、各受光素子から来るはずです。 しかし、それはCCDレシーバーに接続します 電子回路、これにより、各感光素子からその照度に比例した電気信号を抽出できます。

CCD の動作は次のように説明できます。各感光要素 (ピクセル) は、電子の貯金箱のように機能します。 電子は、光源からの光の作用によってピクセルで生成されます。 雨が降ったときの外のバケツのように、一定の期間にわたって、各ピクセルはそれに入る光の量に比例して徐々に電子で満たされます。 この時間の終わりに、各ピクセルに蓄積された電荷がデバイスの「出力」に転送され、測定されます。 これはすべて、光に敏感な要素が配置されている結晶の特定の構造により可能です。 電子回路管理。

CCD マトリックスはほぼ同じように機能します。 露出(投影された画像による照明)の後、デバイスの電子制御回路が複雑な一連のパルス電圧をデバイスに印加します。これにより、ピクセルに電子が蓄積された列がマトリックスの端にシフトし始めます。ここで、同様の測定CCDレジスタが配置され、電荷がすでに垂直方向にシフトされて測定要素に落ち、個々の電荷に比例する信号が生成されます。 したがって、その後の各時点で、蓄積された電荷の値を取得し、それが対応するマトリックス上のピクセル (行番号と列番号) を特定できます。

プロセスの物理学について簡単に説明します。

まず、CCD はいわゆる機能エレクトロニクスの産物であり、個々の無線素子 (トランジスタ、抵抗、コンデンサ) の集合体として表すことはできません。 この作品は、電荷結合の原理に基づいています。 電荷結合の原理は、静電気学から知られている 2 つの位置を使用します。

- 同様の電荷は互いに反発し合う

- 電荷は、ポテンシャル エネルギーが最小の場所に落ち着く傾向があります。 それらの。 無礼に-「魚はより深いところを探しています。」

MOSコンデンサから始めましょう(MOSは金属酸化物半導体の略です)。 これは、MOSFET からドレインとソースを除去した場合に残るものです。つまり、誘電体層によってシリコンから分離された電極だけです。 明確にするために、半導体は p 型であると仮定します。つまり、平衡状態での正孔の濃度は、電子の濃度よりもはるかに (数桁) 大きいと仮定します。 電気物理学では、「正孔」は電子の電荷と逆の電荷です。 正電荷。

このような電極(ゲートといいます)に正の電位をかけるとどうなるでしょうか? ゲートによって生成された電界は、誘電体を介してシリコンを貫通し、移動するホールを反発します。 空乏領域が現れます - 多数キャリアから解放された特定の体積のシリコンです。 CCDに典型的な半導体基板のパラメータでは、この領域の深さは約5μmである。 逆に、ここで光の作用によって発生した電子は、ゲートに引き寄せられ、ゲート直下の酸化物-シリコン界面に蓄積されます。つまり、ポテンシャル井戸に落ちます (図 1)。

米。 一

ゲートに電圧を印加したときのポテンシャル井戸の形成

この場合、電子がウェルに蓄積すると、ゲートによって半導体内に生成された電界が部分的に中和され、最終的にはそれを完全に補償することができます。 電界誘電体にのみ落ち、界面に電子の薄い層が形成されることを除いて、すべてが元の状態に戻ります。

ここで、ゲートの隣に別のゲートを配置し、それに正の電位、さらに最初のゲートよりも大きな正の電位を印加します(図2)。 ゲートだけが十分に近い場合、それらのポテンシャル井戸は結合され、1 つのポテンシャル井戸の電子は、それが「より深い」場合、隣接するポテンシャル井戸に移動します。

米。 2

2 つの近接したゲートの重なり合うポテンシャル井戸。 ポテンシャル井戸が深いところに電荷が流れます。

ここで、一連のゲートがある場合、それらに適切な制御電圧を適用することにより、そのような構造に沿って局所化された電荷パケットを転送できることは明らかです。 CCD の注目すべき特性である自己走査特性は、任意の長さのゲート チェーンを駆動するのにわずか 3 つのクロック バスで十分であるということです。 (エレクトロニクスにおけるバスという用語は導体です。 電流、同じタイプの接続要素、クロックバス-位相シフトされた電圧が送信される導体。)実際、電荷パケットの転送には、3つの電極が必要かつ十分です。1つは送信、1つは受信、もう1つは絶縁、分離相互に受信および送信するペア、および同じ名前のそのようなトリプレットの電極は、1つの外部出力のみを必要とする単一のクロックバスに相互に接続できます(図3)。

米。 3

最も単純な三相 CCD レジスタ。

各ポテンシャル井戸の電荷は異なります。

これは、最も単純な 3 相 CCD シフト レジスタです。 このようなレジスタの動作のクロック図を図 1 に示します。 4.

米。 4

3 相レジスタを制御するためのクロック ダイアグラムは、120 度ずれた 3 つの蛇行です。

電位が変化すると、電荷が移動します。

各時点での通常の動作では、少なくとも 1 つのクロック バスが高い電位を持ち、少なくとも 1 つのクロック バスが低い電位 (バリア ポテンシャル) を持っている必要があることがわかります。 一方のバスで電位が上昇し、もう一方のバスで電位が低下すると (前)、すべての電荷パケットが隣接するゲートに同時に転送され、フル サイクル (各フェーズ バスで 1 サイクル) の間、電荷パケットが 1 つに転送 (シフト) されます。要素を登録します。

電荷パケットを横方向に局在化するために、いわゆるストップチャネルが形成されます。これは、転送チャネルに沿って走る主ドーパントの濃度が増加した狭いストリップです(図5)。

米。 五。

上からレジスターのビュー。

横方向の移送チャネルは、停止チャネルによって制限されます。

事実は、ドーパントの濃度が、空乏領域がその下に形成されるゲート上の特定の電圧を決定するということです(このパラメータは、MOS構造のしきい値電圧にすぎません)。 直感的な考察から、不純物濃度が高いほど、つまり半導体内の正孔が多いほど、それらを深く駆動することが難しくなることは明らかです。つまり、しきい値電圧が高くなるか、ある電圧で電位が低くなりますポテンシャル井戸で。

問題

デジタルデバイスの製造において、結果として得られるデバイスのパラメータに目立った影響を与えることなく、プレート全体のパラメータの広がりが数倍に達する可能性がある場合 (作業は離散的な電圧レベルで行われるため)、CCD では、たとえば、10% のドーパント濃度は、画像ですでに顕著です。 結晶のサイズはそれ自体の問題を追加するだけでなく、メモリLSIのように冗長性が不可能であるため、欠陥領域は結晶全体の使用不能につながります。

結果

CCD マトリックスの異なるピクセルは、技術的に光に対する感度が異なるため、この違いを修正する必要があります。

デジタル CMA では、この補正は Auto Gain Control (AGC) システムと呼ばれます。

AGCシステムのしくみ

簡単にするために、特定のものは取りません。 CCDノードのADCの出力に潜在的なレベルがあると仮定しましょう。 60 - 平均レベル白い。

- CCD ラインの各ピクセルについて、参照白色光で照らされたときに値が読み取られます (より深刻なデバイスでは、「黒レベル」も読み取られます)。

- 値は参照レベル (平均など) と比較されます。

- 出力値と基準レベルの差は、ピクセルごとに保存されます。

- 将来的には、スキャン時にこの差がピクセルごとに補正されます。

AGC システムは、スキャナ システムが初期化されるたびに初期化されます。 マシンの電源を入れると、しばらくするとスキャナ キャリッジが前後に動き始めます (白黒ストリップをクロールします)。 これはAGCシステムの初期化プロセスです。 システムは、ランプの状態 (経年変化) も考慮に入れます。

また、カラースキャナーを搭載した小型複合機では、赤、青、緑の 3 色が順番に「ランプを点灯」することにもお気づきでしょう。 すると原稿のバックライトだけが白くなります。 これは、RGB チャネルごとにマトリックスの感度を個別に適切に修正するために行われます。

ハーフトーン テスト (シェーディングテスト)エンジニアの要求に応じてこの手順を開始し、補正値を実際の状態にすることができます。

これらすべてを実際の「戦闘」マシンで考えてみましょう。 私たちは、よく知られた人気のあるデバイスを基本としています SAMSUNG SCX-4521 (ゼロックス Pe 220)。

なお、弊社の場合はCCDがCIS(Contact Image Sensor)になりますが、根本的に起こっていることの本質はこれからも変わりません。 光源と同じように、LED の列が使用されます。

それで:

CISからの画像信号は約1.2Vのレベルで、デバイスコントローラ(ADCP)のADC部(ADCP)に供給されます。 SADC の後、アナログ CIS 信号は 8 ビットのデジタル信号に変換されます。

SADC のイメージ プロセッサは、最初にトーン補正機能を使用し、次にガンマ補正機能を使用します。 その後、データは動作モードに応じて異なるモジュールに供給されます。 テキストモードでは、画像データは LAT モジュールに送信され、写真モードでは、画像データは「誤差拡散」モジュールに送信され、PC-Scan モードでは、画像データは DMA アクセスを介してパーソナルコンピュータに直接送信されます。

テストする前に、露出ガラスに白い紙を何枚か置きます。 言うまでもなく、光学系、白黒ストライプ、および一般的なスキャナ アセンブリは、最初に内側から「なめる」必要があります。

- TECH MODEで選ぶ

- ENTER ボタンを押して画像をスキャンします。

- スキャン後、「CIS SHADING PROFILE」(CISハーフトーンプロファイル)が印刷されます。 そのようなシートの例を以下に示します。 結果のコピーである必要はありませんが、画像に近いものです。

- 印刷された画像が図に示されている画像と大きく異なる場合は、CIS に障害があります。 レポートシートの下部に「結果:OK」と記載されていますのでご注意ください。 これは、システムが CIS モジュールに対して深刻な主張をしていないことを意味します。 そうしないと、エラー結果が返されます。

プロファイルの印刷例:

頑張って!!

サンクトペテルブルク州立大学 (LSU)、サンクトペテルブルク電気工科大学 (LETI)、Axl の教師の記事と講義の資料が基礎として採用されています。 彼らに感謝します。

V.シェレンバーグが用意した資料

電荷結合素子 (CCD) は、一連の単純な MIS 構造 (金属-誘電体-半導体) であり、金属電極のストリップが線形またはマトリックスの規則的なシステムを形成するように、共通の半導体基板上に形成されます。電極は十分に小さいです (図 41)。 この状況は、デバイスの動作における決定要因が隣接するMIS構造の相互影響であるという事実を決定します。

CCDの動作原理は次のとおりです。 負の電圧が任意の金属 CCD 電極に印加されると、結果として生じる電界の作用の下で、基板内の主なキャリアである電子が表面から離れて半導体の深部に移動します。 表面には、空乏領域が形成されます。これは、エネルギー図上で、少数キャリアのポテンシャル井戸である正孔です。 どういうわけかこの領域に入る正孔は、誘電体と半導体の界面に引き寄せられ、狭い表面近くの層に局在します。

ここで、より大きな振幅の負の電圧が隣接する電極に印加されると、より深いポテンシャル井戸が形成され、正孔がその中を通過します。 必要な制御電圧をさまざまな CCD 電極に印加することにより、さまざまな表面近傍領域での電荷の蓄積と、表面に沿った電荷の指向性移動 (構造から構造へ) の両方を確実に行うことができます。 電荷パケットの導入 (記録) は、例えば極端な CCD 要素 (図 41 の電極 1) の近くに配置された p-n 接合によって、または光生成によって実行できます。 システムからの電荷の除去 (読み取り) も、pn 接合 (図 41 の電極 p) を使用して実行するのが最も簡単です。 したがって、CCDは、外部情報(電気信号または光信号)が移動キャリアの電荷パケットに変換され、表面近くの領域に特定の方法で配置され、情報処理がこれらのパケットの制御された動きによって実行されるデバイスです。表面。 デジタルおよびアナログ システムを CCD に基づいて構築できることは明らかです。 デジタル システムでは、特定の CCD 要素内の正孔の電荷の有無のみが重要です。アナログ処理では、移動する電荷の大きさを扱います。

CCD 動作の設計と物理学は、これらのデバイスの非常に興味深く有用な (そしてしばしばユニークな) 機能の多くを決定します。

CCD の最も重要な機能には、電荷情報を保存する機能が含まれます。 半導体結晶の表面に沿った電荷の直接移動の可能性。 変身の可能性 光束電荷とその後の読み取り (スキャン) に変換します。 CCD の利点は、これらのデバイスの MIS 構造による低消費電力 (情報送信モードで 5 ~ 10 μW/ビット、ストレージ モードでのエネルギー消費がほとんどない) ことです。 構成の単純さと CCD の要素システムの規則性により、これらのデバイスの速度が非常に高速になる可能性があります (特別に設計されたサンプルの場合、制限クロック周波数はギガヘルツ範囲にあります)。

おそらくさらに重要なのは、CCD の設計と技術的な利点です。その主なものは、技術的な明快さと単純さです (デバイスの製造における少数のフォトリソグラフィ、熱拡散、およびエピタキシャルプロセス)。これは、高品質のマルチを作成するための前提条件です。 -要素 (要素数 10 4 -10 6) デバイス; 高度な集積度 (1 チップに 10 5 以上の要素) と高い実装密度 (10 5 ビット/cm 2 以上)。 信頼性の高いシステム構築の決め手となる外部リード数の少なさ。 pn 接合がないこと (CCD のいくつかの pn 接合は「補助」機能を実行し、むしろ「弱い」要件が課せられます)。特に、シリコンと一緒に他の半導体材料を使用する幅広い機会が開かれます (たとえば、ヒ化ガリウム)。

これらの特性はすべて、CCD のさまざまなアプリケーションに大きな可能性をもたらします。

デジタル技術では、シフト レジスタ、ランダム アクセス メモリ、および論理回路が対象となります。 CCD 上のアナログ信号の遅延線 技術仕様音響および磁気の対応物よりも大幅に優れています。

光電子画像変換技術では、CCD は、真空のない半導体ビデオ信号フォーマーを作成するための根本的に新しい可能性を開きます。 それらの固有の自己走査により、電子ビーム走査により、かさばって信頼性の低い高電圧真空管が排除されます。 CCD は CRT のユニークなアナログであり、重量、全体の寸法、および消費電力を削減すると同時に、ビデオ信号フォーマーの信頼性と品質を向上させることができます。 CCD ベースの光検出器の追加の利点は、さまざまな半導体材料を使用する基本的な可能性にあり、これにより、電磁スペクトルの広い領域 (IR 領域を含む) をカバーすることが可能になります。

CCD に基づいた透過型テレビカメラの作成は、将来、技術に信頼性の高い「電子の目」を装備するだけでなく (人間の人工視覚を作成するプロジェクトでは、CCD にも方向付けが行われることに注意してください)、日常生活でのテレビの非常に幅広い使用に。

画像を運ぶ光束が多素子またはマトリックス CCD に向けられると、半導体の大部分で電子正孔対の光生成が始まります。 CCD の空乏領域に入ると、キャリアが分離され、正孔がポテンシャル井戸に蓄積されます (さらに、蓄積された電荷は局所照明に比例します)。 画像認識に十分な時間 (数ミリ秒程度) の後、CCD アレイは照明分布に対応する電荷パケットのパターンを保存します。 クロックパルスがオンになると、電荷パケットが出力リーダーに移動し、電気信号に変換されます。 その結果、出力は、ビデオ信号が与えるエンベロープである、異なる振幅を持つ一連のパルスになります。

これに基づいて、写真電信用のデバイスと送信カメラ(フルフォーマットのカラーテレビカメラまで)を考慮して作成されます。 将来、CCD は、並列情報処理を行う高性能光電子計算機の便利なマトリックス光検出器として応用されるでしょう。

CCD の登場 (1969 年) は、MIS デバイスの物理と技術の分野における研究の結果でした。 半導体技術のこの新しい方向性の開発は、多くの科学チームによって行われています。 さまざまな国すでに注目すべき成果を上げています。

容量が8192、16384、65536ビットで、サンプリング時間が64〜200μs、情報出力レートが1〜5 MHzの高速シングルチップCCDメモリが作成されました。 16K(キロビット)の容量を持つクリスタルに基づいて、256ビットのブロックフェッチで1Mビットの容量を持つメモリが設計されました。 カラーテレビシステムで使用するために、128ビットの容量を持つ広帯域アナログ信号遅延線が開発されました。 CCD ベースの相関器がテストされました。これにより、40,000 個の離散信号値を 1% 未満の合計誤差で同時に処理できます。

多くの米国企業 (主に Bell と RCA) による、分解要素数 200X200 および 500x500 の送信カメラの工業生産の開始について、多数の報告があります。

同時に、途中で気付かないことは不可能です 広く使用されている CCD にはまだ多くの未解決の問題があります。まず第一に、技術的な問題があります。誘電体膜のパンクや電極タイヤの短絡により、十分に大きな情報容量を持ち、高い割合で欠陥のない CCD を取得することはまだできません。収率。 単層メタライゼーションで大型 CCD を作成する際の最も重要な技術的問題は、電極間に狭い (2 ~ 3 μm) ギャップを得ることの問題です。 このような構造の主な技術的欠陥は短絡です。 多層シリコンゲート構造では、ポリシリコンのすべてのレベルの間に高品質の絶縁誘電体を得ることは困難である。

結論として、電荷結合デバイス、特に光電子デバイスに基づくデバイスの作成は、大規模集積回路の開発における重要なステップであり、機能的なマイクロエレクトロニクスへの最初の実際のステップの1つであることに注意したいと思います.

電荷結合デバイス (CCD) は、基板ゲート (CIS 構造) から近接して分離された多数の半導体デバイスであり、その下で少数電荷キャリアの情報パケットをドレインに転送することができます。光放射の吸収のための - からの基板でのソースまたは発生。

CCD の動作原理を、ゲート数の多い MIS トランジスタの構造として表現できる 3 サイクルのシフトレジスタ回路を例に考えます (図 5.9)。 この装置は 3 つのセクションで構成されています。

初め - 入口部 – ソースを含む p + - その下の領域と、拡散からの正孔の移動を制御するための鍵として機能する入力ゲート p+-ソース領域を最初のポテンシャル井戸に。

2番 - 転送セクション – シリコン - 二酸化シリコン界面の電位を制御する一連のゲートで構成されています。 これらのゲートは 2 つを介して相互接続されています。 転送セクションのゲートの電圧は、異なる振幅のパルスの形をしており、周期的な順列で互いに置き換えられます(図5.9、 なれ)。 ゲート電圧がこのように変化すると、ポテンシャル井戸がデバイスの出力に移動し、電荷キャリアのパケット、ホールを一緒に引きずります。

第3 - 出口部 – 含む 区域- 流出遷移。 この遷移は反対方向にシフトされ、それに適したポテンシャル井戸から正孔を抽出するように設計されています (図 5.9、 G).

入力ゲートの下に導電チャネルを形成するのに十分な電圧が、動作の初期サイクルで入力ゲートに印加されるとします ()。 同時に、十分に大きな負の電圧が転送セクションの最初のゲートに存在する場合、つまり 転送セクションの最初のゲートの下にホールの深いポテンシャル井戸がある場合、ホールはソースを離れ、入力ゲートの下のチャネルを通過し、転送セクションの最初のゲートの下のポテンシャル井戸に蓄積します(図.5.9、 6 ).

入力ゲートの電圧は、転送セクションのゲートの電圧を変更する次のサイクルの開始までに除去されます。 したがって、入力ゲートの下の導電チャネルは消失します。 これは、ソースからの注入の結果として、最初のゲートの下のポテンシャル井戸に蓄積された正孔の特定の電荷に対応する情報(たとえば、論理ユニット)が記録される方法です。

論理ゼロに対応する情報を書き込むために、入力ゲートに負電圧を印加してはならないことに注意してください。 この場合、からの正孔の注入はありません。 p + - ソース領域を最初のゲートの下のポテンシャル井戸に (図 5.9, d)そして、電荷キャリアの熱生成、またはデバイスの前のサイクルでのポテンシャル井戸の不完全な空化に関連して、比較的小さな正孔の電荷のみがその中に現れる可能性があります。

転送セクションのゲートの電圧を変更した後、最も負の電圧が 2 番目のゲートにかかるため、正孔のパケットは転送セクションの 2 番目のゲートの下のポテンシャル井戸に移動します (図 5.9、 の)。 転送セクションのゲートで電圧を変更する次のサイクルでは、正孔のパケットはさらに出力セクションに向かって移動します (図 5.9、 日、日).

に適した潜在的なピット内にある場合 R-n- ドレイン接合、電荷キャリアはありません - ホール、そしてドレイン回路の電流に変化はありません。 そして、正孔を含むポテンシャル井戸が近づいた場合のみ 区域- ドレイン接合、これらのホールが抽出され、電流パルスがドレイン回路を通過するか、ドレイン電圧が変化します (図 5.9、 G).

CCD は典型的には動的デバイスであり、より低く、 上限転送セクションに供給される電圧パルスのクロック周波数。

下限クロック周波数

は、表面のポテンシャル井戸の間の事実によって決定されます

電荷キャリアの熱生成に関連する電流であり、原則として、逆抽出電流と変わらない 区域-遷移。 これらの電流は論理ゼロのレベルに影響を与え、空のポテンシャル井戸の正孔の電荷を増加させます。 半導体の温度と特性に応じて、空のポテンシャル井戸に顕著な正孔の蓄積が 100 分の 1 秒から数秒の範囲で発生する可能性があります。 したがって、CCD クロック周波数の下限は、通常単位 - 数十キロヘルツです。

クロック上限 1 つのポテンシャル井戸から別のポテンシャル井戸への電荷の流れの時間 (数ナノ秒程度) によって決まります。 より短い時間では、電荷全体が 1 つのポテンシャル井戸から次のポテンシャル井戸に移動する時間がありません。 したがって、CCD のクロック周波数の上限は通常、数十メガヘルツで決まります。

現在までに、CCD の主な使用分野として次の 3 つが特定されています。

1) 記憶装置;

2)画像を電気信号に変換する装置。

3)アナログ情報処理装置。

ストレージデバイス

動作原理によれば、CCD は遅延線などのストレージ デバイスです。 それらに基づいて、情報の順次入力と出力を備えたデジタルシフトレジスタが作成されました。

情報は、そのようなCCDメモリデバイス内を再生しながら連続的に循環する。 空のポテンシャル井戸のレベルの回復を伴います。 レジスタにアクセスすると、記録された情報は再生成の有無にかかわらずサンプリングされます。 非破壊読み取りまたは記録された情報の破壊。

画像を電気信号に変換するデバイス

このようなデバイスの動作原理は、CCD が半導体に照射されると、その表面近くに電子-ホール電荷キャリアのペアが形成され、ゲートの下のポテンシャル井戸の電界によって分離されるという事実に基づいています。転送セクション。

光量子の吸収中に形成されたキャリアは、CCD の特定の領域の照明に比例してポテンシャル井戸を満たします。 次に、記録された光情報が通常の方法でシフトされると、CCD の出力での信号は照度分布を繰り返します。 画像の行が強調表示されます。 次の行も強調表示できます。 現在、CCD透過カメラは、カラーテレビを含め、解像度の点で通常のテレビ標準に達しています。

アナログ情報処理機器

CCDの助けを借りて、アナログ信号も保存できますが、この場合、記録された情報を再生することは不可能になります。 ただし、CCD を使用すると情報転送の遅延を調整できるため、単純な暗記によって CCD を使用する大きな可能性が開かれます。 アナログ情報を処理するための CCD を使用するための最も単純なオプションは、カラー テレビ受信機用の固定遅延線であることが判明しました。

電荷結合素子 (CCD) は、多数の相互作用する MIS 構造の組み合わせであり、電子の電荷パケットをソースからドレインに転送できます (図 5.19)。 MIS構造の数は数千に達することがあります。 各ゲートの長さは約 10 μm、ゲート間の距離は約 2 μm です。 CCD の動作原理は、MIS 構造の非定常プロセスに基づいています。

Osh.yuojzhzh

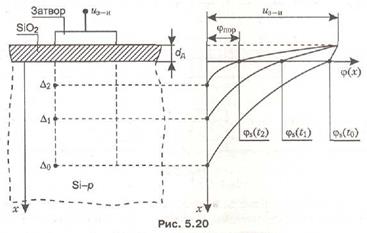

隣接する領域から分離された MIS 構造のゲートの下で発生するプロセスを考えてみましょう。 もしその時 t0ステップ変更ゲート電圧 あなたの子= 0 ~ あなたの子 > あなたは以来、その後、非常に短い期間(誘電緩和時間のオーダー)でゲートの下に厚さD o の空乏層が形成され、そこからゲート電界の作用で正孔が除去されます。 この層は電子にとってのポテンシャル井戸であり、ポテンシャル井戸の深さが深いほど、 うじ。空乏層内の半導体面に垂直な方向のポテンシャル分布を図1に示します。 5.20.

時間が経つにつれて、電荷キャリアの熱生成の比較的ゆっくりとした制御されていないプロセスがゲートの下で発生します。 この場合に形成された正孔は、ゲート電界によってゲート領域から押し出され、負電荷がゲートの下に蓄積され、その結果、表面電位が低下します。 φs空乏層の厚さ Δ

. 時点で t2表面電位が等しくなる ![]() 、その後、逆チャネルが表面に形成され始めます。

、その後、逆チャネルが表面に形成され始めます。

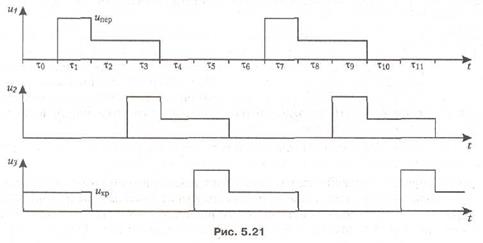

有用な信号に関する情報を運ぶ電荷パケットを形成するために、入力デバイスが使用されます。これは、ソースと基板の間の p-n + 接合 (入力ダイオード) と入力ゲート 3 で構成されます。 半導体結晶の表面に沿って電荷パケットを転送するために、ゲートに段階的な電圧が印加され、2 つを介して相互接続されます (図 5.21)。 電荷パケットを出力信号に変換するために、ドレインとサブストレート間の p-n + ジャンクション (出力ダイオード) と出力ゲート 3 out が使用されます。 CCD 内の電荷パケットの形成、転送、読み取りのプロセスは、図 1 の図に示されています。 図 5.19 は、さまざまな時間間隔での構造に沿った表面電位の分布を示しています。

最初の間隔を取る τ 0 ここで あなた 1- 0, あなた 2- 0, u 3 = および x p =これらの条件下では、ポテンシャル井戸がゲート 3 および 6 の下に存在し、そこに以前に形成された電荷パケットが保存されます。 一部の潜在的なピットには、これらのパッケージがない場合があります。 この区間のソース電位は、基板のn + 領域とir領域との間の接触電位差に等しい。 ドレイン電位が高く、 φ~ = φ k0 + u,どこ と -電源から印加される逆電圧 E i.p抵抗を通して R n.

その合間に τ 1電荷パケットは第 1 ゲートの下で形成され、電荷パケットは第 3 ゲートの下から第 4 ゲートに転送され、電荷パケットは第 6 ゲートの下から読み取られます。

電荷パケットを形成するために、転送電圧が最初のゲートに印加されます あなたの車線= 20-25 V、負の電圧パルスがソースに印加され、入力ダイオードが順方向にオンになり、正の制御信号電圧が入力ゲートに印加され、その結果、電子が入力の下に注入されますゲートを通過し、最初のシャッターの下のより深いポテンシャル井戸に移動します。 電荷パケットの値は、信号電圧と制御パルスの持続時間に依存します。 信号電圧がゼロの場合、電荷パケットは形成されません。

3 番目のゲートの下から 4 番目のゲートへの電荷パケットの転送は、4 番目のゲートが転送電圧を受け取るという事実によるものです。 あなた 1= あなたの車線、これは保存電圧よりも大きい u 3 = および x p 3 番目のゲートに作用し、その結果、4 番目のゲートの下のポテンシャル井戸は 3 番目のゲートよりも深くなります。 したがって、電荷パッケージは第 4 ゲートの下のより深いポテンシャル井戸に移動します。

情報の読み取りは、正の電圧パルスが出力ゲートに印加され、その下に、最後の (6 番目の) ゲートよりも深いポテンシャル井戸が形成されるため、電子が出力ゲートの下に入り、次にドレイン。 ドレイン回路に電流パルスが現れ、回路の出力に負の電圧パルスが現れます。 最後のゲートの下にパケットがない場合、ドレイン回路の電流はゼロです。

その合間に τ2電荷パケットはゲート 1 と 4 の下に格納されます。 τ 3電荷パケットはゲート 2 と 5 の下を移動します。 τ4電荷パケットはゲート 2 と 5 の下に格納されます。 5電荷パケットはゲート 3 と 6 の下を移動します。 τ6電荷パケットは、間隔と同じ方法でゲート 3 と 6 の下に格納されます。 τ 0 . 次に、プロセスが繰り返され、電荷パケットが半導体結晶の表面に沿って順次移動します。

CCD は通常、動的デバイスであるため、クロック周波数の上限と下限があります。

クロック周波数の下限は、制御されていない電子によるポテンシャル井戸の充填によって決まります。 半導体の温度と特性に応じて、空のポテンシャル井戸にかなりの量の電子が蓄積することが、100 分の 1 秒から数秒の範囲の時間で発生する可能性があります。 電荷パケットの許容蓄積時間を長くするには、電荷キャリアが生成されるトラップの濃度や温度などを下げます.CCD クロック周波数の下限は 30 ~ 300 Hz の範囲にあります。

クロック周波数の上限は、電荷が 1 つのポテンシャル井戸から別のポテンシャル井戸に流れる時間によって決まります。この時間は数ナノ秒です。 より短い時間では、電荷パケットは 1 つのポテンシャル井戸から別のポテンシャル井戸に移動する時間がありません。 したがって、クロック周波数の上限は数十メガヘルツです。

考えられる動作原理から、CCD は遅延線型のメモリ デバイスであり、クロック パルスの周波数を変更することによって遅延時間を調整できるため、CCD をコンピュータのメモリ デバイスとして使用することができます。 CCDに基づいて、電荷形式で提示されるデジタル信号の複雑な処理のためのデバイスを構築できます。 現在、超小型回路は、加算、減算、乗算、アナログからデジタル、デジタルからアナログへの信号変換に CCD を使用して作成されています。 CCD はアナログ信号も保存できます。 これを行うには、料金パケットの値が値に十分であることを確認する必要があります。 アナログ信号、これは概略的に簡単に実装できます。

電荷パケットの形成は、前述のように注入だけでなく、MIS構造が作成された結晶表面を照射することによっても実行できます。これは、画像を電気信号に変換するためにテレビで応用されています。 このようなCCDの動作原理は、CCDがゲートの下のポテンシャル井戸に照射されると、CCDの対応するセクションの照射に比例する電子の電荷パケットが形成されるという事実に基づいている。 その後、電荷パケットが通常の方法でシフトされると、CCD の出力での信号は、MIS 構造の水平チェーンに沿って照明分布を繰り返します。 そのような水平チェーンの数は、送信されたテレビ画像のライン数と等しくなければなりません。

現在、ゲートに三相電源を供給しているCCDに比べて、より高度なデバイスが作られています。 これらには、フローティング ゲート構造に基づく CCD、MNOS 構造に基づく CCD、隠しチャネルと 2 フェーズ制御を備えた CCD、およびその他多数が含まれます。 これらのタイプのデバイスでは、製造技術を簡素化し、ゲート間の距離を減らすことができました。 それらの情報の保存時間は数万時間に達します。

1. 絶縁ゲートを持つ電界効果トランジスタと制御 p-n 接合を持つトランジスタの違いは何ですか?

2. 閾値電圧とは何ですか? また、それは何に依存していますか?

3. 飽和電圧とは何ですか? また、それは何に依存していますか?

4. 制御と出力の特性を描いて説明できる 電界効果トランジスタ.

5. 電界効果トランジスタの微分パラメータがどのように決定されるかを示します。

6. FET の等価回路を描いて説明せよ。

8. 電界効果トランジスタの周波数範囲と速度を制限する物理現象は何ですか?

9. 電界効果トランジスタがパルスモードで動作しているときの電流と電圧のタイミング図を描いて説明してください。

10. 電界効果トランジスタの勾配をバイポーラの勾配と比較します。

11.電荷結合素子の動作原理を説明してください。